”出租车计价器 Verilog“ 的搜索结果

出租车计费器一般都是都是按公里计费,通常是起步费为 X1(12)元(X1 元可以行走 A(3)公里),超过起步费后每公里价格 X2(2)元,超过 B(10) 公里,每公里价格 X3(3)元。所以要完成一个出租车计费器,就需要...

该资源针对NEXYS开发板设计,程序修改xdc后可适用于其他开发板;包含插拔钥匙、开关车门等部分的模拟,此外可通过里程与中途停留时间相结合的计费方式。程序经过下板验证,安全可靠!

启动键start表示汽车启动,起步价7元,同时路程开始计数,停止键stop表示熄火,车费和路程均为0,当暂停键pause为1时,车费和路程停止计数,当档位分别取0,1,2,3,时路程计数逐渐加快,路程超过3...--出租车状态机控制。

基于Verilog_HDL设计的出租车计价器.doc

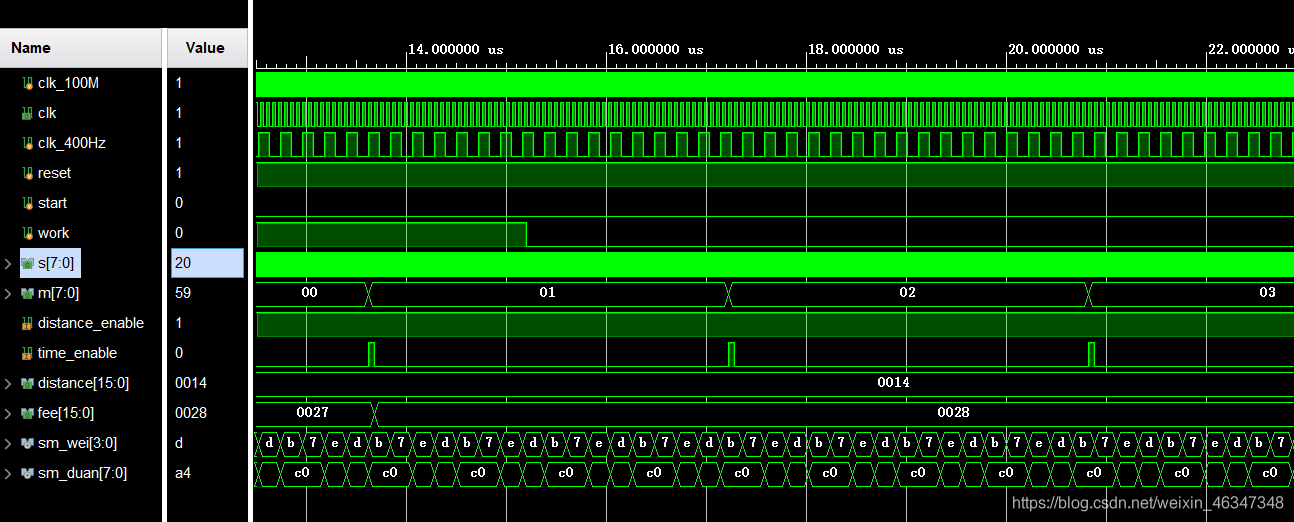

出租车计价器verilog及modelsim仿真波形,拿来直接当课设使用,货真价实!

以下是出租车计价器的Verilog设计要求: 1. 使用计数器来模拟出租车里程的计算,每个脉冲信号表示汽车前进100米。 2. 设计一个状态机来控制计价器的状态转换,包括起步价状态、每公里计费状态、等待计费状态等。 3. ...

有关出租车计价器的设计,您可以参考引用中的功能描述,根据这些功能描述来设计Verilog源程序。您需要考虑如何根据行程距离和等待时间来计算费用,并将这些逻辑转化为Verilog代码。另外,您还需要考虑如何使用脉冲...

/(2)费用的计算及显示,出租车的起步价设为7.00元,当里程小于2km时,按起步价计算费用;费用显示方式为XXX,单位为元;//(2)费用的计算及显示,出租车的起步价设为7.00元,当里程小于2km时,按起步价计算费用;...

出租车计价器由以下几个模块组成: 1、速度产生模块 module velocity(clk,rst,en_1,en_2,F_1HZ,frequency ); 2、速度判断模块 module judge_v(rst,frequency,F_1HZ,en_1,en_2,v_h,v_l); 3、路程模块 module ...

2.1 , 出租车计价器的要求 : ◇ 出租车起步价为8元,行驶过程中大于两公里后每公里1元,中途停止等待时间累计大于三分钟后按每3分钟1元计价 。 ◇ 计价系统里程显示范围为:099公里,分辨率1公里。计价费用显示...

出租车计费器,起步价10元,3公里内起步价,可以切换白天和夜晚计费,白天时超过3公里后2.4元每公里,停车时6元每10分钟;output [5:0] bit_select//低电平点亮,低电平选通。input day_night,//白天夜晚,0:夜晚 1...

上海大学 硬件大作业 出租车计价器 已经实现老师要求的全部功能,放心食用 环境:Quartus 6.0

通过Verilog语言设计和实现一个出租车计价器,我们可以轻松将其嵌入在嵌入式系统中。通过该计价器,出租车司机和乘客可以方便地了解行驶情况和计价信息,提高出租车服务的效率和质量。在嵌入式系统中,我们可以使用...

设计要求:设计一个出租车计价器。该计价器的计费系统:行程 3公里内,且等待累计时间2...本文档中详述了基于FPGA的出租车计价器设计,所用语言是Verilog,开发环境是 Xilinx 14.6,其中包括各个模块的完整代码及解释。

以轮胎半径为计算距离的计价器,对于大学生相关课程有帮助,本人用quartus 8.0 做的,含测试波形模拟,仅供参考

代码功能: 出租车计费器 1、起步价5元,3公里内起步价 2、3公里后每公里2.1元 3、停车等待时,0.6元每十分钟 4、计费方式可以通过代码参数快捷修改

本文将以Verilog和VHDL为基础,详细介绍如何设计一个嵌入式的出租车计价器电路,并附上相应的源代码。计数器的值可以通过时钟信号的频率与时间单位进行换算,从而得到实际的行驶时间和里程。输入输出控制模块负责...

课程设计-基于FPGA的出租车计价器系统.zip课程设计-基于FPGA的出租车计价器系统.zip课程设计-基于FPGA的出租车计价器系统.zip课程设计-基于FPGA的出租车计价器系统.zip课程设计-基于FPGA的出租车计价器系统.zip课程...

名称:出租车计费器Basys2开发板verilog出租车计价器出租车打表器(代码在文末下载)软件:ISE语言:Verilog代码功能:设计一个出租车计费器,能在 Basys2开发板上实际运行 1、用开发板上的2个按键输入路程和计时...

基于某VerilogHDL设计地出租车计价器.pdf基于某VerilogHDL设计地出租车计价器.pdf基于某VerilogHDL设计地出租车计价器.pdf基于某VerilogHDL设计地出租车计价器.pdf基于某VerilogHDL设计地出租车计价器.pdf基于某...

2.内容:【提供操作视频】vivado2019.2平台中通过verilog开发的出租车自动计费器,具有行车里程计费,等候时间计费等功能 3.用处:用于出租车自动计费器算法编程学习 4.指向人群:本硕博等教研学习使用 5.运行注意...

使用Verilog硬件描述语言编写的出租车计价器,编写环境为Quartus ii 9.0,硬件平台为Cyclone EP1C6Q240C8. 实现主要功能如下: -输入时钟为系统晶振50Mhz. -两个开关分别控制:开始/停止计费,出租车行进中/停止等待...

基于FPGA的出租车计价器系统源码.zip > * 软件环境: Quartus 13.1 > * 仿真环境: Modelsim > * 编程语言: Verilog HDL > * 芯片型号: Altera Cyclone IVE EP4CE10F17C8 **系统具有如下基础功能:** * 1、当行程小于...

乘客乘坐出租车时,其费用分成起步价、行车里程费和等候时间费三部分,由自动计费器自动记录。在汽车行进时向自动计费器发送脉冲信号,在一定的公里数(即一定的脉冲数)内,按起步价计费超过这一里程后,自动计费器按里程...

module fp50m(clk,reset,newclk,newclk1);input clk,reset;output newclk,newclk1;reg newclk,newclk1;reg [31:0] count,count1;always@(posedge clk or negedge reset)beginif(!reset)begin newclk;...

推荐文章

- Python Django 版本对应表以及Mysql对应版本_django版本和mysql对应关系-程序员宅基地

- Maven的pom.xml文件结构之基本配置packaging和多模块聚合结构_pom <packaging>-程序员宅基地

- Composer 原理(二) -- 小丑_composer repositories-程序员宅基地

- W5500+F4官网TCPClient代码出现IP读取有问题,乱码问题_w5500 ping 网络助手 乱码 send(sock_tcps,tcp_server_buff,-程序员宅基地

- Python 攻克移动开发失败!_beeware-程序员宅基地

- Swift4.0_Timer 的基本使用_swift timer 暂停-程序员宅基地

- 元素三大等待-程序员宅基地

- Java软件工程师职位分析_java岗位分析-程序员宅基地

- Java:Unreachable code的解决方法_java unreachable code-程序员宅基地

- 标签data-*自定义属性值和根据data属性值查找对应标签_如何根据data-*属性获取对应的标签对象-程序员宅基地